# Operating Systems: A Linux Kernel-Oriented Approach

(Partially written. Updates are released every week on Fridays.) Send bug reports/suggestions to srsarangi@cse.iitd.ac.in Version 0.51

Smruti R. Sarangi

April 29, 2024

This work is licensed under a Creative Commons Attribution-NoDerivs 4.0 International License. URL: https://creativecommons.org/licenses/by-nd/4.0/deed.en

# List of Trademarks

• Microsoft and Windows are registered trademarks of Microsoft Corporation.

# Contents

| 1        | Intr | oducti   | on                                               | <b>7</b> |

|----------|------|----------|--------------------------------------------------|----------|

|          | 1.1  | Types    | of Operating Systems                             | 9        |

|          | 1.2  | The Li   | inux OS                                          | 10       |

|          |      | 1.2.1    | Versions, Statistics and Conventions             | 11       |

| <b>2</b> | Bas  | ics of ( | Computer Architecture                            | 15       |

|          | 2.1  |          | Registers and Interrupts                         | 15       |

|          |      | 2.1.1    | Multicore Systems                                | 15       |

|          |      | 2.1.2    | Inside a Core                                    | 16       |

|          |      | 2.1.3    | Registers                                        | 17       |

|          |      | 2.1.4    | Interrupts, Exceptions, System Calls and Signals | 19       |

|          | 2.2  | Virtua   | l Memory                                         | 24       |

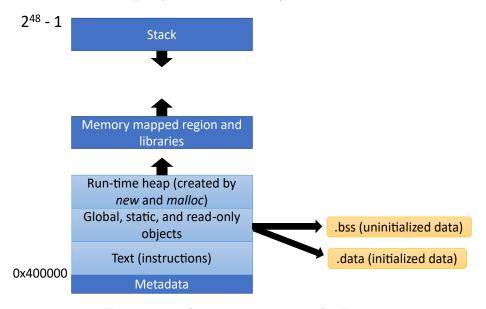

|          |      | 2.2.1    | Memory Map of a Process                          | 27       |

|          |      | 2.2.2    | Idea of Virtual Memory                           | 28       |

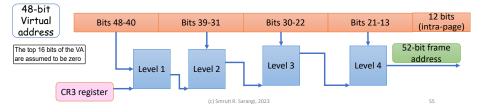

|          |      | 2.2.3    | Implementation of the Address Translation System | 32       |

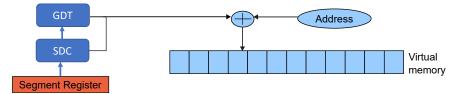

|          |      | 2.2.4    | Segmented Memory                                 | 38       |

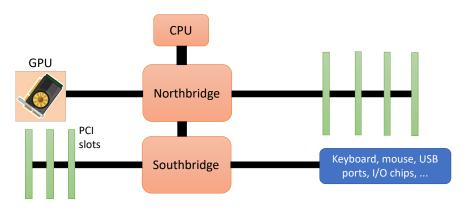

|          | 2.3  | I/O Sy   | rstem                                            | 40       |

|          |      | 2.3.1    | Overview                                         | 41       |

|          |      | 2.3.2    | I/O via I/O Ports                                | 42       |

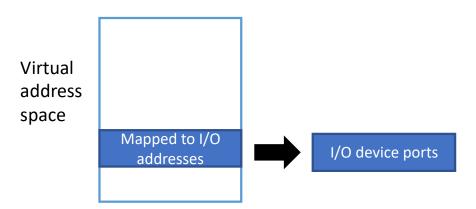

|          |      | 2.3.3    | Memory-Mapped I/O                                | 43       |

|          |      | 2.3.4    | I/O using DMA                                    | 44       |

| 3        | Pro  | cesses   |                                                  | 47       |

| -        | 3.1  |          | otion of a Process                               | 48       |

|          | 3.2  |          | rocess Descriptor                                | 48       |

|          | 0.2  | 3.2.1    | struct task_struct                               | 48       |

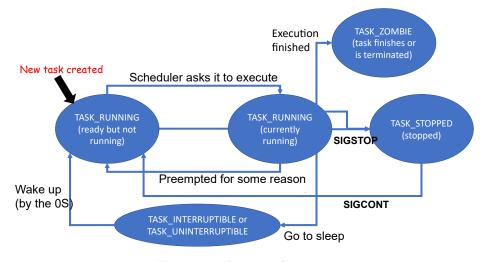

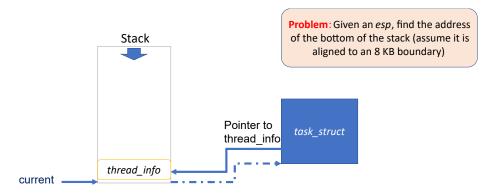

|          |      | 3.2.2    | struct thread_info                               | 49       |

|          |      | 3.2.3    | Task States                                      | 51       |

|          |      | 3.2.4    | Kernel Stack                                     | 53       |

|          |      | 3.2.5    | Task Priorities                                  | 55       |

|          |      | 3.2.6    | Computing Actual Task Priorities                 | 56       |

|          |      | 3.2.7    | sched_info                                       | 57       |

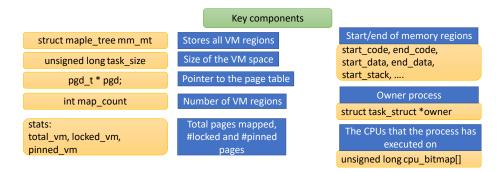

|          |      | 3.2.8    | Memory Management                                | 58       |

|          |      | 3.2.9    | Storing Virtual Memory Regions                   | 59       |

|          |      | 3.2.10   | The Process Id                                   | 60       |

|          |      | 3.2.11   | Processes and Namespaces                         | 61       |

|          |      | 3.2.12   | File System, I/O and Debugging Fields            | 66       |

|          |      | 3.2.13   | The PTrace Mechanism                             | 67       |

|   | 3.3 | Process Creation and Destruction                                            | 37  |

|---|-----|-----------------------------------------------------------------------------|-----|

|   |     | 3.3.1 The Fork Mechanism                                                    | 38  |

|   |     | 3.3.2 The exec Family of System Calls                                       | 73  |

|   |     |                                                                             | 74  |

|   | 3.4 |                                                                             | 75  |

|   | 0.1 | 0                                                                           | 75  |

|   |     |                                                                             | 76  |

|   |     | v I                                                                         | 78  |

|   |     |                                                                             |     |

|   |     | 3.4.4 The Context Switch Process                                            | 30  |

| 4 | Sve | tem Calls, Interrupts, Exceptions and Signals 8                             | 33  |

| 4 | 4.1 |                                                                             | 34  |

|   | 4.1 |                                                                             |     |

|   |     | 1 0 0                                                                       | 35  |

|   |     | 0                                                                           | 35  |

|   |     | 0                                                                           | 36  |

|   | 4.2 | 1 1                                                                         | 37  |

|   |     |                                                                             | 38  |

|   |     | •                                                                           | 90  |

|   |     | 4.2.3 Kernel Code for Interrupt Handling                                    | 93  |

|   |     | 4.2.4 Managing the IDT Table                                                | 94  |

|   |     | 4.2.5 The Interrupt Path                                                    | 96  |

|   |     | 4.2.6 Exceptions                                                            | 97  |

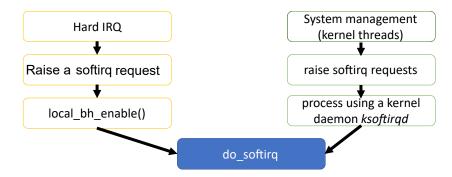

|   | 4.3 | Softirqs, Threaded IRQs, Work Queues                                        | )1  |

|   |     | 4.3.1 Softirgs                                                              |     |

|   |     | 4.3.2 Threaded IRQs                                                         |     |

|   |     | 4.3.3 Work Queues                                                           |     |

|   | 4.4 | Signal Handlers                                                             |     |

|   | т.т | 4.4.1 Example of a Signal Handler                                           |     |

|   |     | 4.4.2 Signal Delivery                                                       |     |

|   |     |                                                                             |     |

|   |     | 4.4.3 Kernel Code                                                           |     |

|   |     | 4.4.4 Entering and Returning from a Signal Handler 11                       | 10  |

| 5 | Swn | chronization and Scheduling 11                                              | a   |

| 0 | 5.1 | Synchronization                                                             |     |

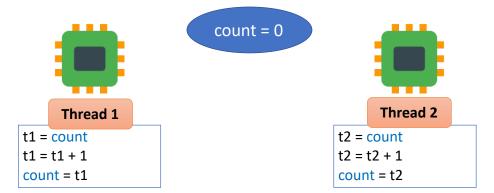

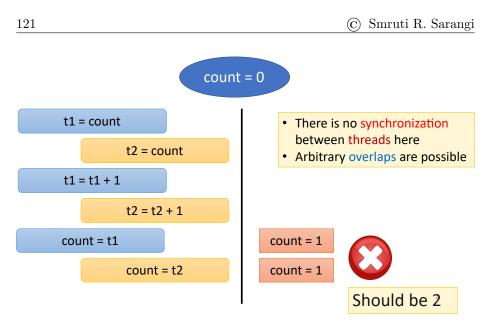

|   | 0.1 | 5.1.1 Introduction to Data Races                                            |     |

|   |     |                                                                             |     |

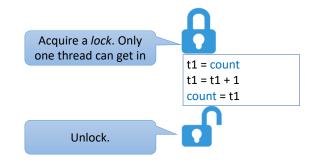

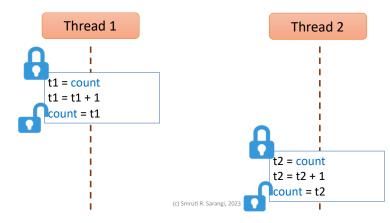

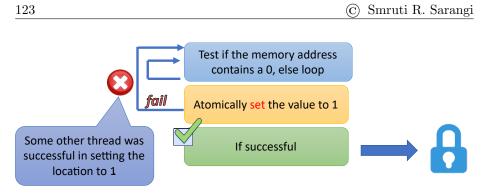

|   |     | 5.1.2 Design of a Simple Lock $\ldots$ 12                                   |     |

|   |     | 5.1.3 Theory of Data Races                                                  |     |

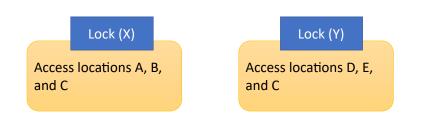

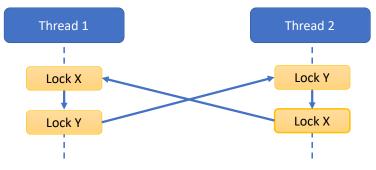

|   |     | 5.1.4 Deadlocks                                                             |     |

|   |     | 5.1.5 Pthreads and Synchronization Primitives                               |     |

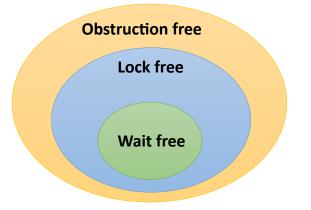

|   |     | 5.1.6 Theory of Concurrent Non-Blocking Algorithms 13                       |     |

|   |     | 5.1.7 Progress Guarantees                                                   | 39  |

|   |     | 5.1.8 Semaphores $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $14$ | 12  |

|   |     | 5.1.9 Condition Variables                                                   | 13  |

|   |     | 5.1.10 Reader-Writer Lock                                                   | 14  |

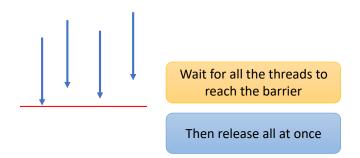

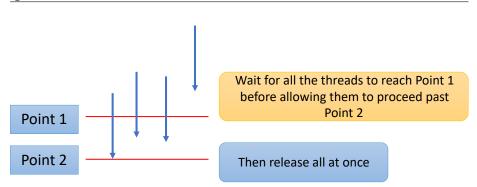

|   |     | 5.1.11 Barriers and Phasers                                                 | 15  |

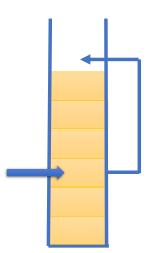

|   | 5.2 | Queues                                                                      | 17  |

|   |     | 5.2.1 Wait-Free Queue                                                       |     |

|   |     | 5.2.2 Queue with Mutexes                                                    | -   |

|   |     | 5.2.3 Queue with Semaphores                                                 |     |

|   |     | 5.2.4 Queue with Semaphores but No Busy Waiting                             |     |

|   |     | 0.2.4 Queue with beinaphores but to Dusy waiting                            | ± ، |

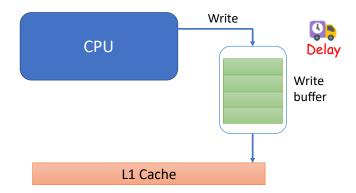

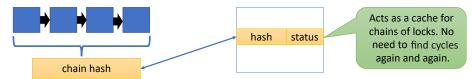

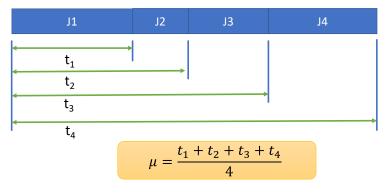

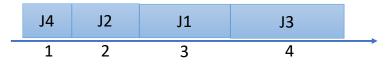

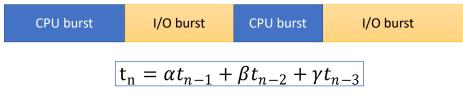

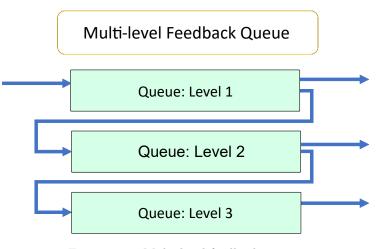

|   | 5.3<br>5.4 | 5.2.5       Reader-Writer Lock       153         Concurrency within the Kernel       154         5.3.1       Kernel-Level Locking: Spinlocks       155         5.3.2       Kernel Mutexes       160         5.3.3       Kernel Semaphores       162         5.3.4       The lockdep Mechanism       162         5.3.5       The RCU Mechanism       164         Scheduling       165       165         5.4.1       Space of Scheduling Problems       165         5.4.2       Single Core Scheduling       167 |

|---|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6 | The        | 5.4.3Multicore Scheduling1725.4.4Banker's Algorithm1755.4.5Scheduling in the Linux Kernel1805.4.6Completely Fair Scheduling (CFS)1855.4.7Real-Time and Deadline Scheduling190                                                                                                                                                                                                                                                                                                                                  |

| 0 | 6.1        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

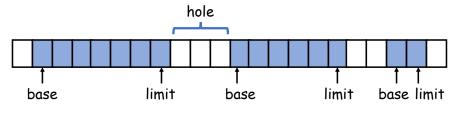

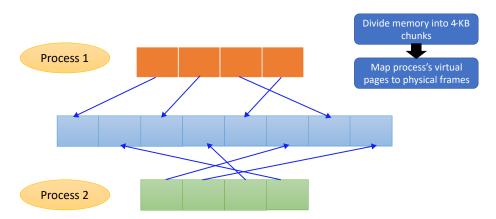

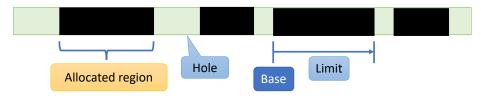

|   | 0.1        | Traditional Heuristics for Page Allocation1916.1.1Base-Limit Scheme191                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   |            | 6.1.2       Classical Schemes to Manage Virtual Memory 193                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

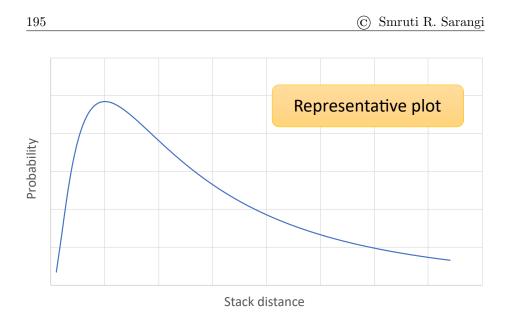

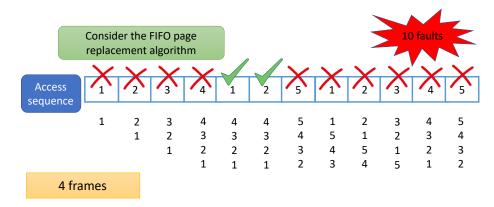

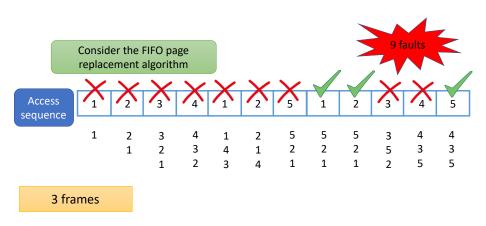

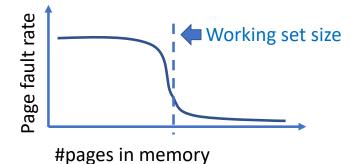

|   |            | 6.1.3 The Notion of the Working Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   | 6.2        | Virtual and Physical Address Spaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

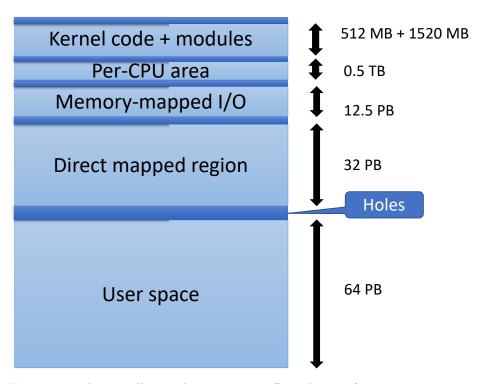

|   | 0.2        | 6.2.1 The Virtual Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

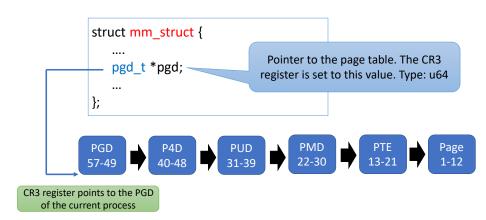

|   |            | 6.2.2         The Page Table         205                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   |            | 6.2.3   Pages and Folios   208                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   |            | 6.2.4 Managing the TLB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

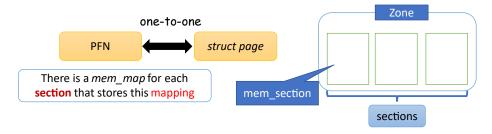

|   |            | 6.2.5 Partitioning Physical Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | 6.3        | Page Management in the Kernel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   | 6.4        | Kernel Memory Allocation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

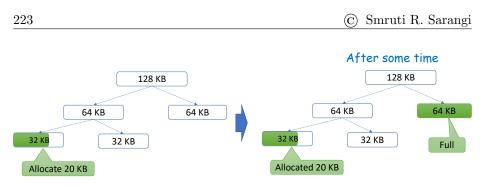

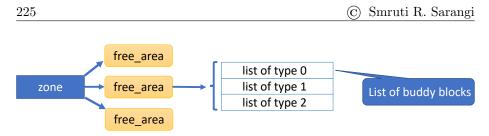

|   |            | 6.4.1 Buddy Allocator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

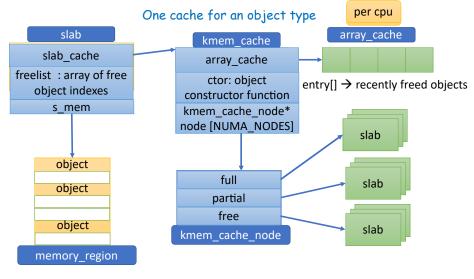

|   |            | 6.4.2 Slab Allocator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

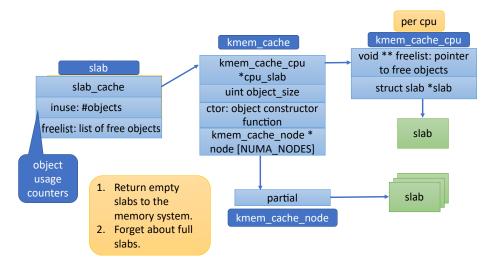

|   |            | 6.4.3 Slub Allocator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 7 | The        | I/O System and Device Drivers 231                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 8 | Virt       | ualization and Security 233                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   | <b>T</b>   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Α |            | X86-64 Assembly Language 235                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

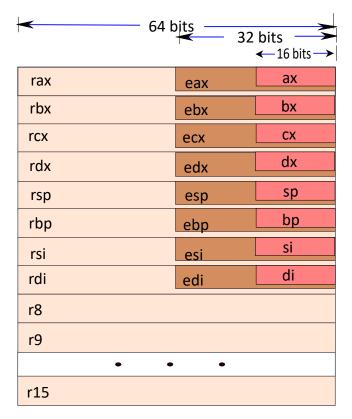

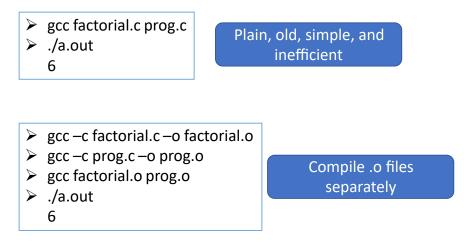

|   | A.1        | Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   | A.2        | Basic Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

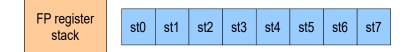

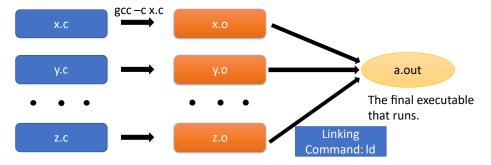

| в |            | ppiling, Linking and Loading 241                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   | B.1        | The Process of Compilation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   |            | B.1.1 Compiler Passes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

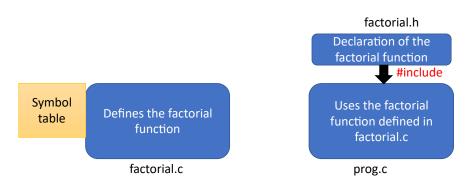

|   |            | B.1.2 Dealing with Multiple C Files                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   | DO         | B.1.3 The Concept of the Header File                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   | B.2        | The Linker                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

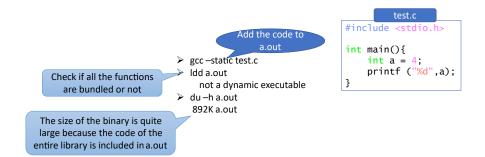

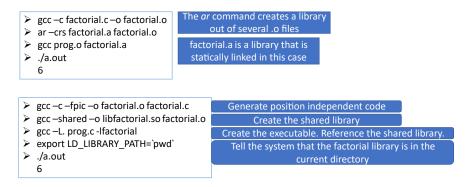

|   |            | B.2.1 Static Linking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

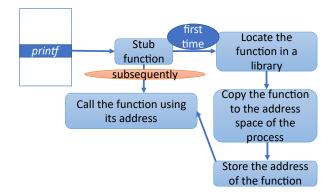

|   |            | B.2.2 Dynamic Linking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   |            | B.2.3 The ELF Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|              | B.3 | Loader                                 |

|--------------|-----|----------------------------------------|

| $\mathbf{C}$ | Dat | a Structures 255                       |

|              | C.1 | Linked Lists in Linux                  |

|              |     | C.1.1 Singly-Linked Lists              |

|              | C.2 | Red-Black Tree                         |

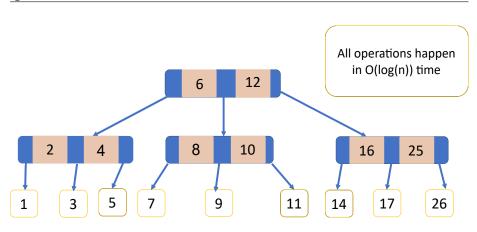

|              | C.3 | B-Tree                                 |

|              |     | C.3.1 The Search Operation             |

|              |     | C.3.2 The Insert and Delete Operations |

|              |     | C.3.3 B+ Tree                          |

|              | C.4 | Maple Tree                             |

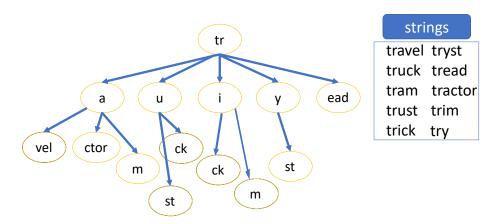

|              | C.5 | Radix Tree                             |

|              |     | C.5.1 Patricia Trie                    |

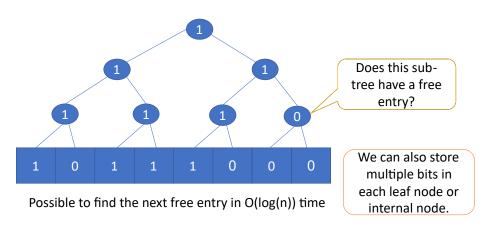

|              | C.6 | Van Emde Boas Tree                     |

|              |     |                                        |

# Chapter 1 Introduction

Welcome to the exciting world of operating systems. An operating system – commonly abbreviated as an OS – is the crucial link between hardware and application programs. We can think of it like a class monitor whose job is to manage the rest of the students (to some extent). In this case, it is a special program, which exercises some control over hardware and other programs. In other words, it has special features and facilities to manage all aspects of the underlying hardware and to also ensure that a convenient interface is provided to high-level application software such that they can seamlessly operate oblivious to the idiosyncrasies of the underlying hardware. The basic question that needs to be answered is, "What is the need for having a specialized program for interacting with hardware and also managing the normal C/Java/Python programs that we write?"

We need to start out with understanding that while designing hardware, our main goals are power efficiency and high performance. Providing a convenient interface to programs is not a goal and also should not be a goal. We do not want normal programs to have access to the hardware because of security concerns and also because any otherwise benevolent, inadvertent change can actually bring the entire system down. Hence, there is a need for a dedicated mechanism to deal with hardware and to also ensure that any operation that potentially has security implications or can possibly bring the entire system down, is executed in a very controlled fashion. This is where the role of the OS becomes important.

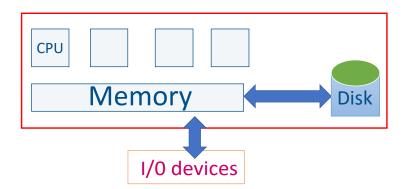

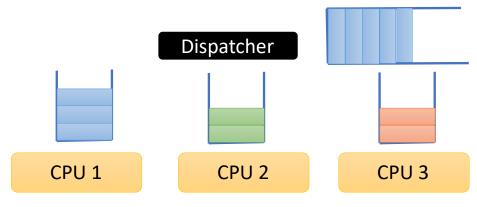

Figure 1.1 shows the high-level design of a simple computer system. We can see the CPUs, the memory and the storage/peripheral devices. These are, broadly speaking, the most important components of a modern hardware system. An OS needs to manage them and needs to make it very easy for a regular program to interact with these entities.

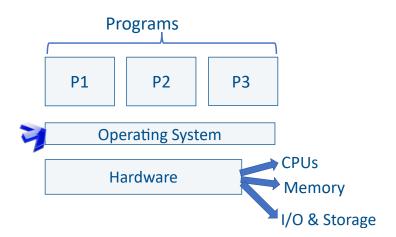

The second figure (Figure 1.2) shows the place of the OS in the overall system. We have the underlying hardware, high-level programs running on top of it and the OS sits in the middle. It acts as a mediator, a broker, a security manager and an overall resource manager. Let us thus quickly summarize the need for having a special program like an OS.

• Programs share hardware such as the CPU, the memory and storage devices. These devices have to be fairly allocated to different programs based on user-specified priorities. The job of the OS is to do a fair resource al-

Figure 1.1: Diagram of the overall system

Figure 1.2: Place of the OS in the overall system

location with predefined priorities in mind.

- There are common resources in the system, which multiple programs may try to access concurrently. There is a need to regulate this process such that such concurrent accesses are disciplined and it is not possible for one resource to be used in parallel by multiple programs when that was not the original intention.

- Different devices have different methods and protocols for managing them. It is essential to speak their language and ensure that high-level commands are translated to device-level commands. This responsibility cannot be put on normal programs. Hence, we need specialized programs within the OS (device drivers) whose job is to exclusively interact with devices.

- Managing the relationships between programs and shared resources such as the memory is fairly complex. For instance, we can have many running programs that are trying to access the same set of memory locations. This may be a security violation or this may be a genuine shared memory-based

communication pattern. There is a need to differentiate one from the other by providing neat and well-defined mechanisms.

• Power, temperature and security concerns have become very important over the last decade. The reason being that any operating system that is being designed today also needs to run on very small devices such as mobile phones, tablets and even smart watches. In the foreseeable future, they may run on even smaller devices such as smart glasses or may even be embedded within the body. Hence, it is important for an OS to make it possible for the administrator to configure different power policies, which it must strictly adhere to.

#### Definition 1

An operating system (OS) works as a CPU manager, memory manager, device manager and storage manager. Its job is to arbitrate accesses to these resources and ensure that programs execute in a secure fashion and their performance is maximized subject to power and temperature constraints.

# 1.1 Types of Operating Systems

We can have different kinds of operating systems based on the target hardware. For instance, we can have operating systems for large high-performance machines. In this case, they would be optimized to execute a lot of scientific workloads and also participate in distributed computing scenarios. On the other hand, operating systems for desktop/laptop machines need to keep the requirements for general-purpose users in mind. It is expected that regular users will use OSes for running programs such as web browsers, word processors, email clients and for watching videos or playing games. Given the highly heterogeneous nature of such use cases, there is a need to support a large variety of programs and also a large variety of devices. Hence, in this case more flexibility is desirable. And clearly, for such situations, the chances of viruses or malware attacks are elevated. Hence, security is a first-order concern.

The next important usage scenario for an operating system is a mobile device. Nowadays, almost all mobile devices starting from phones to tablets have an operating system installed. For all practical purposes, a mobile device is a full-fledged computer, albeit with reduced hardware resources. However, a mobile phone operating system such as Android needs to be extremely efficient in terms of both power and performance. The reason is that we don't have a lot of resources available and battery capacity is a major constraint. As a result, the focus should be on optimizing battery life yet providing a good quality of experience.

Operating systems are also making their way into much smaller devices such as smart watches. Here, we don't expect a lot of applications, but we expect the few applications that run on such watches to operate seamlessly. We expect that they will work under severe power constraints and deliver. Furthermore, in this case the port size and the memory footprint of the OS needs to be very small.

# 1.2 The Linux OS

In this course, will be teaching generic OS concepts in the context of the Linux OS. As compared to all other operating systems, Linux has a very different history. It is not been written by one particular person or one particular organization. In fact, it is a modern marvel in the sense that it has been written via a massive worldwide collaboration comprising a very large number of individuals who would otherwise not have been connected with each other. This is truly a remarkable effort and a great example of people coming together to create something that is beneficial to all. Given that the code is open source, and the OS itself is freely available, it now has widespread acceptance in all kinds of computing platforms ranging from smart watches to laptops to high-end servers.

It all started with Linus Torvalds, a student in Helsinki, Finland, who wanted to work on a freely available version of a variant of the then popular UNIX operating system (Minix). Given the fact that most versions of UNIX those days were proprietary and were beyond the reach of students, he decided to create an operating system for his Intel-based machine that was a rival of Minix, which was primarily developed and meant to be used in an academic setting. Over the next few years, this activity attracted a lot of developers for whom this was more of a hobby than a profession. All of them contributed little bit of code and some of them contributed in other ways as well such as testing the operating system or porting it to new hardware. At the same time, the free software movement was also taking shape. Under the GNU (GNU is not Unix) umbrella, a lot of software, specifically utilities, were being developed. The Linux developers found a common cause with the developers in the free software movement and were able to incorporate many of the utilities that they developed into the Linux operating system. This was a good fusion of communities, which led to rapid development of the new OS.

Way back in 1992, Linux was released under the GNU Public license (GPL) [License, 1989]. Believe it or not, The unique nature of the GPL license had a fair amount of impact on the popularity of Linux. It was a free-to-use license similar to many other licenses that were prevalent at that time. Like other free software licenses, it allowed the user to freely download/distribute the code and make modifications. However, there was an important caveat, which distinguished GPL from other licenses. It was that it is not possible for any redistributing entity to redistribute the code with a more restrictive license. For instance, if let's say someone downloads the Linux code, then it is not possible for her to make proprietary changes and then start selling the OS. This was explicitly forbidden. This ensured that whatever changes and modifications are made to any piece of code that comes with a GPL license, all the changes are visible to the community and thus they can build on this. There were no proprietary walls; this allowed the community to make rapid progress. However, at that point of time, this was not the case with other pieces of software. Users or developers were not duty-bound to contribute back to the mother repository.

Over the years, Linux grew by leaps and bounds in terms of functionality and popularity. By 2000, it had established itself as a worthy desktop and server operating system. People started taking it seriously and many academic groups started moving away from UNIX to adopt Linux. Note that Linux was reasonably similar to UNIX in terms of the interface and some high-level design decisions. The year 2003 was a pivotal year for Linux, because this year, Linux kernel version 2.6 was released. It had a lot of changes and was very different from the previous kernel versions. After this, Linux started being taken very seriously in both academic and enterprise circles. In a certain sense, it had entered the big league. Many companies sprang up that started offering Linux-based offerings, which included the kernel bundled with a set of packages (software programs) and also custom support. Red  $Hat((\widehat{\mathbf{R}}))$ ,  $Suse((\widehat{\mathbf{R}}))$  and  $Ubuntu((\mathbf{R}))(Canonical((\mathbf{R})))$  where some of the major vendors that dominated the scene. As of writing this book, circa 2023, these continue to be major Linux vendors. Since 2003, a lot of other changes have also happened. Linux has found many new applications - it has made major inroads into the mobile and handheld market. The Android operating system, which as of 2023 dominates the entire mobile operating space is based on Linux. Many of the operating systems for smart devices and other wearable gadgets are also based on Android. In addition,  $Google(\widehat{\mathbf{R}})$ 's Chrome OS also is a Linux-derived variant. So are other operating systems for Smart TVs such as  $LG(\mathbb{R})$ 's webOS and Samsung( $\mathbb{R}$ )'s Tizen.

As of today, Linux is not the only free open source operating system. There are many others, which are derived from classical UNIX, notably the Berkeley standard distribution (BSD) variant. Some of the important variants are FreeBSD, OpenBSD and NetBSD. Similar to Linux, their code is also Three to use and distribute. Of course, they follow a different licensing mechanism. however, they are also very good operating systems in their own right. They have their niche markets and they have a large developer community that actively adds features and puts them to new hardware. The paper by Singh et al. [Singh and Sarangi, 2020] nicely compares the three operating systems in terms of performance for different workloads (circa 2015).

## **1.2.1** Versions, Statistics and Conventions

In this book, we will be primarily teaching generate OS concepts. however, every operating system concepts needs to be explained in the light of a solid practical implementation. This is where the latest version of the current as of 2023 will be used. Specifically we will use kernel version v6.2 explain OS concepts. All the OS code that we shall show will be from the main terminal branch. It is available at https://elixir.bootlin.com/linux/v6.2.16/source/kernel.

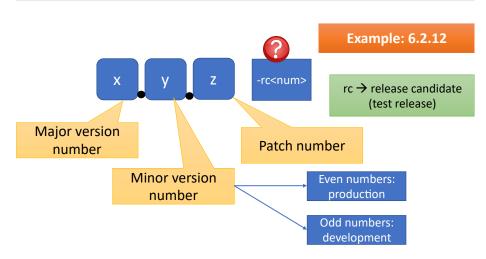

Let us now go through some of the key statistics vis-a-vis The Linux kernel version v6.2 has roughly 25 million lines of source code. Every version change typically adds 250,000 lines of source code. The numbering scheme For the kernel version numbers is shown in Figure 1.3.

Consider a Linux version 6.2.16. Here 6 is the major version, 2 is the minor version number and 16 is the patch number. Every  $\langle major, minor \rangle$  version pair has multiple patch numbers associated with it. Every time there is a major commit, a patch is created. If a minor version number is even, then it means that it is a production version. This version can be released to the public and can be used for regular applications (desktop or enterprise). Odd numbers are development versions where new features and the effects of bug fixes are

Figure 1.3: Logic for assigning Linux versions

incorporated. Such a patch is considered to be *stable*. It is a non-trivial feature addition and is considered to be stable.

Each such patch is associated with multiple release candidates. A release candidate does not have major bugs; however, it incorporates multiple smaller fixes and feature additions that are not fully verified. These release candidates are still considered experimental and are not fully ready to be used in any kind of a production-level setting. They are numbered as follows -rc1, -rc2, .... They are mainly aimed at other Linux developers. They can download these release candidates, test their features, suggest improvements and initiate a process of (mostly) online discussion. Once, the discussions have converged, the release candidates can be succeeded by a stable version (read patch or major/minor version).

#### Details of the Linux Code Base

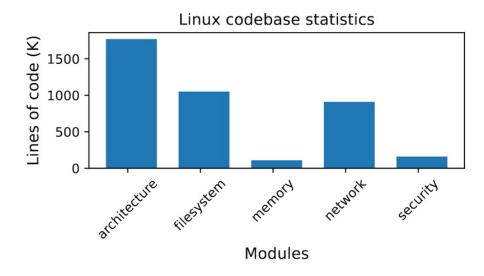

Let us now provide an overview of the Linux code base (see Figure 1.4). The architecture subsystem of the kernel contains all the code that is architecture specific. The Linux kernel has a directory called *arch* that contains various subdirectories. Each subdirectory corresponds to a distinct architecture such as x86, ARM, Sparc, etc. An OS needs to rely on processor-specific code for various critical actions like booting, device drivers and access to privileged functions. All of this code is nicely bundled up in the *arch* directory. The rest of the code of the operating system is independent of the architecture. It is not dependent on the ISA or the machine. It relies on primitives, macros and functions defined in the corresponding *arch* subdirectory. All the operating system code relies on these abstractions such that developers do not have to concern themselves with details of the architecture such as whether it is 16-bit or 32-bit, little endian or big endian, CISC or RISC. This subsystem contains more than 1.5 million lines of code.

The other large subsystems that contain large volumes of code are the directories for the filesystem and network. Note that a popular OS such as Linux need to support a large number of file systems and network protocols. As a

Figure 1.4: Breakup of the Linux code base

result, the code base for these directories is quite large. The other subsystems for the memory and security modules are comparatively much smaller.

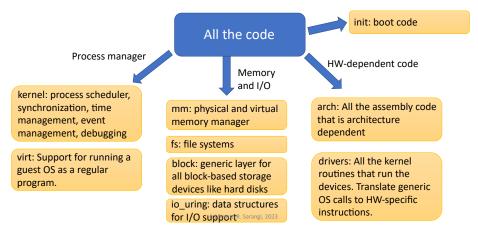

Figure 1.5: Important directories in the Linux kernel code base

Figure 1.5 shows the list of prominent directories in the Linux kernel. The *kernel* directory contains all the core features of the Linux kernel. Some of the most important subsystems are the scheduler, time manager, synchronization manager and debugging subsystem. It is by far the most important subsystem or the core kernel. We will focus a lot on this subsystem.

We have already seen the *arch* directory. A related directory is the *init* directory that contains all the booting code. Both these directories are hardware dependent.

The mm, fs, block and io\_uring directories contain important code for the

memory subsystem, file system and I/O modules. These modules are related to the code to virtualize the operating system *virt*, where we can run the OS as a regular program on top of another OS. The virtualization subsystem is tightly coupled with the memory, file and I/O subsystems .

Finally, the largest directory is *drivers* that contains drivers (specialized programs for talk to devices) for a host of I/O devices. Of course, there are multiple things to be considered here. We don't want to include the code of every single device on the planet in the code base of the kernel. It will become too large. At the same time, there is an advantage. The kernel can seamlessly run on a variety of hardware. Hence, the developers of the kernel need to wisely choose the set of drivers that they need to include in the code base that is released and distributed. The devices should be very popular and the drivers should be deemed to be safe (devoid of security issues).

# Chapter 2

# Basics of Computer Architecture

An operating system is the connecting link between application programs and hardware. Hence, it is essential that any serious student of operating systems gains a fair understanding of programming languages and the way programs are written, and the way hardware is designed (computer architecture). The aim of this chapter is to outline the fundamentals of computer architecture that are needed to understand the working of an operating system. This chapter does not aim to teach the student computer architecture. The student is requested to consult traditional textbooks on computer architecture [Sarangi, 2021, Sarangi, 2023] for getting a deeper understanding of all the concepts. The aim of this chapter is to provide an overview such that the student can recapitulate all the important concepts and understand some of the key hardware features that modern OSes rely on.

# 2.1 Cores, Registers and Interrupts

## 2.1.1 Multicore Systems

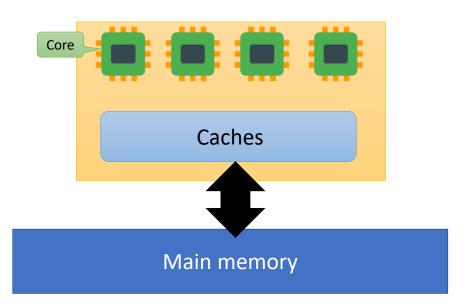

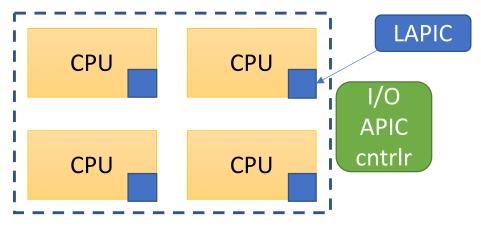

Figure 2.1 shows an overview of a typical multicore processor. As of 2023, a multicore processor has anywhere between 4-64 cores, where each core is a fully functional pipeline. Furthermore, it has a hierarchy of caches. Each core typically has an instruction cache (i-cache) and a data cache (d-cache or L1 cache). These are small yet very fast memories ranging from 8 KB to 64 KB. Then, we have an L2 cache and possibly an L3 cache as well, which are much larger. Depending upon the type of the processor, the size of the L3 cache's size can go up to several megabytes. Some of the very recent processors are including an additional L4 cache as well. However, that is typically on a separate die housed in the same multichip module, or on a separate layer (in a 3D chip).

The last level of the cache (known as the LLC) is connected to the main memory, which is quite large (8 GB to 1 TB as of 2023) and needless to say the slowest of all. It is typically made up of DRAM memory cells that are slow yet have a very high storage density. The most important point that we need to keep in mind here is that it is only the main memory (DRAM memory located outside

Figure 2.1: A multicore processor

the chip) that is visible to software, notably the OS. The rest of the smaller memories inside the chip such as the L1, L2 and L3 caches are not visible to the OS and for all practical purposes, the OS is oblivious of them. Some ISAs have specialized instructions that can flush certain levels of the cache hierarchy either fully or partially. Sometimes even user applications can use these instructions. However, this is the only notable exception. Otherwise, we can safely assume that almost all software including privileged software like the operating system are unaware of the caches. Let us live with the assumption that the highest level of memory that an OS can see or access is the main memory.

A software program including the OS perceive the memory space to be one large array of bytes. Any location in this space can be accessed at will and also can be modified at will. Of course, later on when we discuss virtual memory, we will have to change this abstraction. But, even then, large parts of this abstraction will continue to hold.

# 2.1.2 Inside a Core

Let us now take a sneak peek inside a core. A core is a fully-featured pipeline, which can either be a regular in-order pipeline or an out-of-order pipeline. Furthermore, each core has some amount of cache memory: L1-level instruction and data caches. The core also has a set of named storage locations that are accessible by instructions directly known as *registers*. The advantage of having these registers that number between 8 to 32, is that they can be accessed very quickly by instructions, often in a fraction of a cycle. All the registers are stored in a register file, which is made up of SRAMs; it is significantly faster than caches that typically take multiple cycles to access. Register File

Most of the operations in a core happen on the registers. Registers are often both the operands and even when a location in memory needs to be accessed, it is accessed using values stored in registers. For instance, in the 32-bit x86 ISA, the expression mov %eax, 4(%esp) stores the value in the eax register into the memory location that is stored in the %esp register plus 4. As we can see, registers are ubiquitous. They are used to access memory addresses and as we shall see later, I/O address as well. Let us differentiate between CISC and RISC processors there. RISC processors tend to use registers much more than CISC processors that have a fair number of memory operands in their instructions. In any case, registers are central to the operation of any program (be it RISC or CISC), and needless to say the compiler needs to be aware of them.

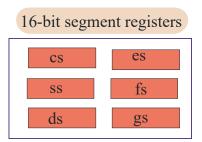

## 2.1.3 Registers

#### **General Purpose Registers**

Let us look at the space of registers in some more detail. All the registers that regular programs use are known as *general purpose registers*. These are visible to all software including the compiler. Note that almost all the programs that are compiled today will use registers and the author is not aware of any compilation model or any architectural model that does not rely on registers.

#### **Privileged Registers**

A core also has a set of registers known as *privileged* registers, which only the OS can see. In Chapter 8, we will also look at hypervisors or virtual machine managers (VMMs) that also run with OS privileges. All such software are known as system software or privileged mode software. They are given special treatment by the CPU. They can access privileged registers.

For instance, an ALU has a *flags* register that stores its state especially the state of instructions that have executed in the past such as comparison instructions. Often these *flags* registers are not visible to regular applicationlevel software. However, they are visible to the OS and anything else that runs with OS privileges such as VMMs. It is necessary to access these registers to enable multi-tasking: run multiple programs on a core one after the other.

We also have control registers that can enable or disable specific hardware features such as the fan, LED lights on the chassis and turn of the system itself. We do not want all of these instructions to be visible to regular programs because then a single application can create havoc. Because of this, we entrust only a specific set of programs (OS and VMM) with access to these registers.

There are debug registers that are meant to debug hardware and system software. Given the fact that they are privy to more information and can be used to extract information out of running programs, we do not allow regular programs to access these registers. Otherwise, there will be serious security violations. However, from a system designer's point of view or from the OS's point of view these are very important. This is because they give us an insight into how the system is operating before and after an error is detected – this can potentially allow us to find the root cause of bugs.

Finally, we have I/O registers that are used to communicate with externally placed I/O devices such as the monitor, printer, network card, etc. Here again, we need privileged access. Otherwise, we can have serious security violations and different applications may try to monopolize an I/O resource and not allow

other applications to access them. Hence, the OS needs to act as a broker and this is possible only why access to the device needs to be restricted.

Given the fact that we have discussed so much about privileged registers, we should now see how the notion of privileges is implemented and how we ensure that only the OS and related system software such as the VMM can have access to privileged resources such as the privileged registers.

#### **Current Privilege Level Bit**

Along with registers, modern CPUs also store the current mode of execution. For instance, we need to store the state/mode of the current CPU, which basically says whether it is executing operating system code or not. This is because if it is executing OS code, then we need to enable the executing code to access privileged registers and also issue privileged instructions. Otherwise, if the CPU is executing normal application-level code, then access to these privileged registers should not be allowed. Hence, historically processors always have had a bit to indicate the status of the program that they are executing, or alternatively the mode that they are in. This is known as the *Current Privilege Level* or *CPL* bit. In general, a value equal to zero indicated a privileged mode (the OS is executing) and a value of one indicated that an application program is executing.

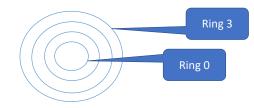

Figure 2.2: Rings in x86 processors

Modern-day processors typically have more modes of execution. Intel processors, for instance, have four modes of execution, which are also known as rings – Ring 0 (OS) to Ring 3 (application) (refer to Figure 2.2). The primary role of rings 1 and 2 is to run guest operating systems and other software that do not require as much of privileged access as the software running in ring zero. Nevertheless, they will have enjoy more privileges than regular application code. They are typically used while running guest OSes on virtual machines.

#### Privileged and Non-Privileged Instructions

Most instructions are non-privileged. This means that they are regular load-/store, arithmetic, logical and branch instructions. These instructions can be executed by all types of code including the application and the OS. These instructions can also seamlessly execute when the OS is executing as a guest OS on a virtual machine.

Recall that we also discussed privileged instructions, when we discussed privileged registers. These are specialized instructions that allow the program to change the internal state of the processor like changing its frequency or accessing certain features that a regular program should never have access to. These include control registers, debug registers and I/O registers.

We will ask an important question here and answer it when we shall discuss virtual machines in Chapter 8. What happens when application code or code at a lower privilege level (higher ring) accesses instructions that should be executed by code at a higher privilege level (lower ring)? In general, we would expect that there will be an exception. Then the appropriate exception handler will take over and take appropriate action. If this is the case, we shall see in Chapter 8 that writing a virtual machine is reasonably easy. However, there are a lot of instructions in the instruction sets of modern processors that do not show this behavior. Their behavior is far more confusing and pernicious. They yield different results when executed in different modes without generating exceptions. We shall see that handling such instructions is quite difficult and that is why the design of virtual machines is actually quite complicated. The main reason for this is that when instructions were created initially while designing the ISA, virtual machines were not around and thus designers could not think that far enough. As a result, they thought that having such polymorphic instructions (instructions that change their behavior based on the ring level) was a good idea. When virtual machines started gaining prevalence, this turned out to be a huge problem.

#### 2.1.4 Interrupts, Exceptions, System Calls and Signals

The discussion in this chapter up till now should have convinced the reader that an application program in itself is quite incompetent. For instance, it does not have access to large parts of the hardware and also does not have a lot of control on its own execution or the execution of other processes. Hence, there is a necessity to actively engage with the underlying operating system. There are different ways by which the operating system and application communicate. Let us quickly go through them.

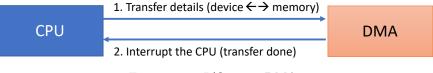

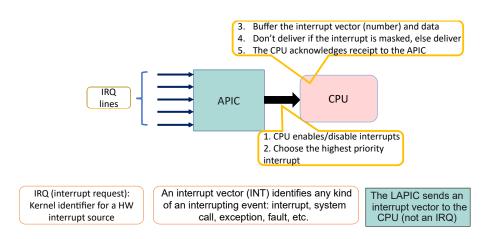

- **Interrupts** An interrupt is a specialized message sent to the processor via an I/O controller, which corresponds to an external hardware event such as a key press or the arrival of a network packet. In this case, it is important to draw the attention of the CPU Such that it can process the interrupt. This would entail stopping the execution of the currently executing program and jumping to a memory location that contains the code of the *interrupt handler* (specialized routine in the OS to handle the interrupt).

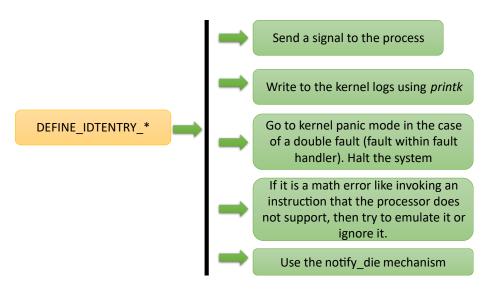

- **Exception** An exception corresponds to some kind of an error in the execution of the program. This could be an event such as dividing by zero, issuing an illegal instruction or accessing an address that is not mapped to main memory. In this case, an exception is generated, which is handled by a corresponding exception handler (part of the OS code).

- **System Call** If an application needs some service from the OS such as creating a file or sending a network packet, then it cannot use the conventional mechanism, which is to make a function call. OS functions cannot directly be invoked by the application. Hence there is a need to generate a dummy interrupt such that The same set of actions can take place, which happens

when an external interrupt is received. In this case, a specialized system call handler takes over and satisfies the request made by the application.

Signal A system call is a message that is sent from the application to the OS. A signal is the reverse. It is a message that is sent from the OS to the application. An example of this would be a key press. In this case, an interrupt is generated, which is processed by the OS. The OS reads the key that was pressed, and then figures out the process that is running in the foreground. The value of this key needs to be communicated to this process. The signal mechanism is the method that is used. In this case, a function registered by the process with the OS to handle a "key press" event is invoked. The running application process then gets to know that a certain key was pressed and depending upon its logic, appropriate action is taken. A signal is basically a *callback function* that an application registers with the OS. When an event of interest happens (pertaining to that signal), the OS calls the callback function in the application context. This callback function is known as the *signal handler*.

As we can see, communicating with the OS does require some novel and unconventional mechanisms. Traditional methods of communication that include writing to shared memory or invoking functions are not used because the OS runs in a separate address space and also switching to the OS is an onerous activity. It also involves a change in the privilege level and a fair amount of bookkeeping is required at both the hardware and software levels, as we shall see in subsequent chapters.

#### Example of a System Call

Let us provide a brief example of a system call. It is in fact quite easy to issue, even though application developers are well advised to not directly issue system calls mainly because they may not be sure of the full semantics of the call. Furthermore, operating systems do tend to change the signature of these calls over time. As a result, code that is written for one version of the operating system may not work for a future version. Therefore, it is definitely advisable to use library calls like the standard C library (glibc), which actually wrap the system calls. Library calls almost never change their signature because they are designed to be very flexible. Flexibility is not a feature of system calls because parameter passing is complicated. Consequently, library calls remain portable across versions of the same operating system and also across different variants of an operating system such as the different distributions of Linux.

In the header file /usr/include/asm/unistd\_64.h, 286 System calls are defined. The standard way to call a system call is as follows.

```

mov $<sys call number>$, %rax

syscall

```

As we can see, all that we need to do is that we need to load the number of the system call in the **rax** register. The **syscall** Instruction subsequently does the rest. We generate a dummy interrupt, store some data corresponding to the state of the executing program (for more details, refer to [Sarangi, 2021]) and load the appropriate system call handler. An older approach is to directly generate an interrupt itself using the instruction int 0x80. Here, the code 0x80 stands for a system call. However, as of today, this method is not used for x86 processors.

#### Saving the Context

The state of the running program is known as its *context*. Whenever, we have an interrupt, exception or a system call, there is a need to store the context, jump to the respective handler, finish some additional work in the kernel (if there is any), restore the context and start the original program at exactly the same point. The caveat is that all of this needs to happen without the explicit knowledge of the program that was interrupted. Its execution should be identical to a situation where it was not interrupted by an external event. Of course, if the execution has led to an exception or system call, then the corresponding event/request will be handled. In any case, we need to return back to exactly the same point at which the context was switched.

Figure 2.3: The "context save" process

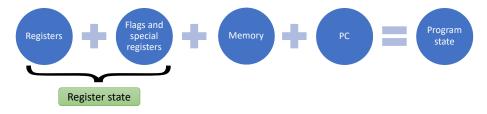

Figure 2.3 show an overview of the process to store the context of a running program. The state of the running program comprises the contents of the general purpose registers, contents of the flags and special purpose registers, the memory and the PC (program counter). Towards the end of this chapter, we shall see that the virtual memory mechanism stores the memory state very effectively. Hence, we need not bother about storing and restoring the memory state because there is already a mechanism namely virtual memory that takes care of it completely. Insofar as the rest of the three elements are concerned, we can think of all of them as the volatile state of the program that is erased when there is a context switch. As a result, a hardware mechanism is needed to read all of them and store them in memory locations that are known a priori. We shall see that there are many ways of doing this and there are specialized/privileged instructions that are used.

For more details about what exactly the hardware needs to do, readers can refer to the computer architecture text by your author [Sarangi, 2021]. In the example pipeline in the reference, the reader will appreciate the need for having specialized hardware instructions for automatically storing the PC, the flags and special registers, and possibly the stack pointer in either privileged registers or a dedicated memory region. Regardless of the mechanism, we have a known location where the volatile state of the program is stored and it can later on be retrieved by the interrupt handler. Note that for the sake of readability, we will use the term interrupt handler to refer to a traditional interrupt handler as well as exception handlers and system call handlers wherever this is clear from the

#### context.

Subsequently, the first task of the interrupt handler is to retrieve the program state of the executing program – either from specialized registers or a dedicated memory area. Note that these temporary locations may not store the entire state of the program, for instance they may not store the values of all the general purpose registers. The interrupt handler will thus have to be more work and retrieve the full program state. In any case, the role of the interrupt handler is to collect the full state of the executing program and ultimately store it somewhere in memory, from where it can easily be retrieved later.

Restoring the context of a program is quite straightforward. We need to follow the reverse sequence of steps.

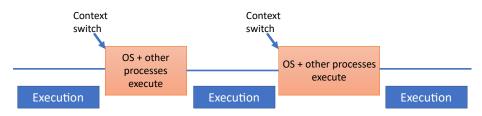

The life cycle of a process can thus be visualized as shown in Figure 2.4. The application program executes, it is interrupted for a certain duration after the OS takes over, then the application program is resumed at the point at which it was interrupted. Here, the word "interrupted" needs to be understood in a very general sense. It could be a hardware interrupt, a software interrupt like a system call or an exception.

Figure 2.4: The life cycle of a process (active and interrupted phases)

We can visualize this situation as follows. The OS treats an application as an *atomic entity* that can be moved from core to core, suspended at any point of time and resumed later, possibly on the same core or on a different core. It is a fully self-contained entity that does not carry any baggage from its execution on a previous core (from a correctness point of view). The context save and restore process is thus very effective – it fully saves the running state of the process such that it can be restored at any point of time later.

#### Timer Interrupts

There is an important question to think about here. What if there is a program that does not see any interrupts and there are no system calls or exceptions? This means that the OS will never get executed if all the cores are occupied by different instances of such programs. Kindly note that the operating system is never executing in the background (as one would want to naively believe) – it is a *separate program* that needs to be invoked by a very special method namely either a system call, exception or interrupt. Let us refer to system calls, exceptions and interrupts as *events of interest*. It cannot come into the picture (execute on a core) any other way. Now, we are looking at a very peculiar situation where all the cores are occupied with programs that do none of the above. There are no events of interest. The key question that we need to answer is whether the system becomes unresponsive and if these programs decide to run

for a long time, is rebooting the system the only option?

#### Question 1

Assume we have a situation, where we have a single-core machine and the program that is running on the core is purely computational in nature. It does not make any system calls and it also does not lead to any exceptions. Furthermore, assume that there is no hardware or I/O activity and therefore no interrupts are generated. In such a situation, the process that is running on the core can potentially run forever unless it terminates on its own. Does that mean that the entire system will remain unresponsive till this process terminates? We will have a similar problem on a multicore machine where there are k cores and k regular processes on them, where no events of interest are generated.

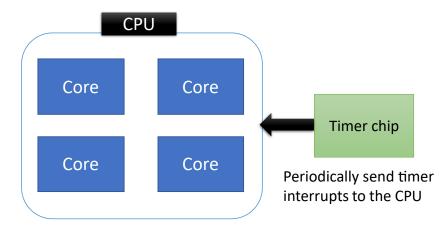

This is a very fundamental question in this field. Can we cannot always rely on system calls, exceptions and interrupts (events of interest) to bring in the operating system. This is because as we have shown in question 1, it is indeed possible that we have a running program that does not generate any events of interest. In such a situation, when the OS is not running, an answer that the OS will somehow swap out the current process and load another process in its place is not correct. A core can run only one process at a time, and if it is running a regular application process, it is not running the OS. If the OS is not running on any core, it cannot possibly act.

Figure 2.5: The timer chip generates periodic interrupts

We need to thus create a mechanism to ensure that the OS periodically runs regardless of the frequency of events of interest. This mechanism is known as a timer interrupt. As shown in Figure 2.5, there is a separate timer chip on the motherboard that periodically sends timer interrupts to the CPU. There is a need for such a chip because we need to have a source of dummy interrupts. Whenever, a timer interrupt is generated, it is routed to one of the cores, there is a context switch and the OS starts executing. This is how the OS periodically comes in even when there is no other event of interest. All platforms that support an operating system need to have a timer chip. It is arguably the most integral part of the machine that supports an operating system. The key insight is that this is needed for ensuring that the system is responsive and it periodically executes the OS code. The operating system kernel has full control over the processes that run on cores, the memory, storage devices and I/O systems. Hence, it needs to run periodically such that it can effectively manage the system and provide a good quality of experience to users.

Listing 2.1: Jiffies source : include/linux/jiffies.h extern unsigned long volatile jiffies;

We divide time into *jiffies*, where there is a timer interrupt at the end of every *jiffy*. The number of jiffys (jiffy count) is incremented by one when a timer interrupt is received. The duration of a jiffy has been reducing over the course of time. It used to be 10 ms in the Linux kernel around a decade ago and as of 2023, it is 1 ms. It can be controlled by the compile time parameter HZ. If HZ=1000, it means that the duration of a jiffy is 1 ms. We do not want a jiffy to be too long, otherwise the system will take a fair amount of time to respond. Simultaneously, we also do not want it to be too short, otherwise a lot of time will be spent in servicing timer interrupts.

#### Inter-processor interrupts

As we have seen, the OS gets invoked on one core and now its job is to take control of the system and basically manage everything including running processes, waiting processes, cores, devices and memory. Often there is a need to ascertain if a process has been running for a long time or not and whether it needs to be swapped out or not. If there is a need to swap it out, then the OS always chooses the most eligible process (using its scheduler) and runs it on a core.

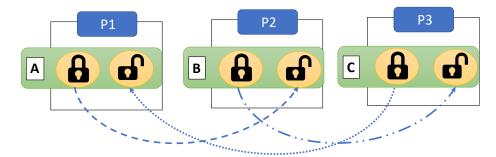

If the new process runs on the core on which the OS is executing, then it is simple. All that needs to be done is that the OS needs to load the context of the process that it wants to run. However, if a process on some other core needs to be swapped out, and it needs to be replaced with the chosen process, then the process is more elaborate. It is necessary to send an interrupt to that core such that the OS starts running on that core. There is a mechanism to do so – it is called an inter-processor interrupt (or IPI). Almost all processors today, particularly all multicore processors, have a facility to send an IPI to any core with support from the hardware's interrupt controller. Relevant kernel routines frequently uses such APIs to run the OS on a given core. The OS may choose to do more of management and bookkeeping activities or quickly find the next process to run and run it on that core.

# 2.2 Virtual Memory

The first question that we would like to ask is how does a process view the memory space? Should it be aware of other processes and the memory regions that they use? Unless we provide an elegant answer to such questions, we will entertain many complex corner cases and managing memory will be very difficult. We are in search of simple abstractions.

One large array of bytes

Figure 2.6: The way that a programmer or compiler view the memory space

Such a simple abstraction is shown in Figure 2.6. A process simply views the entire memory space as a sequence of bytes. For instance, in a 32-bit architecture, a process assumes that it can access any of the  $2^{32}$  bytes at will. Similarly, in a 64-bit architecture, a process assumes that it can access any of the  $2^{64}$  bytes at will. The same assumption is made by the programmer and the compiler. In fact, a large part of the pipeline and the CPU also make the same assumption. If we think about it, we cannot make any other assumption; this is the most elegant and simplifies the job of everybody other than the engineers designing the memory system. The complexity of the memory system stems from the fact that in any ISA, load and store instructions primarily read their addresses from registers. They can add a constant offset to it, however, the fact still remains that most of the address information comes from registers. The size of a register thus determines the range of addresses that can be accessed.

#### The Compatibility Problem

This is why in an *n*-bit architecture, where the register size is *n* bits, the most straightforward thing to assume is that the instructions can access any of the addressable  $2^n$  bytes. A similar assumption needs to be made by the programmer and the compiler because they only see registers. Other details of the memory system are not directly visible to them.

Note that a program is compiled only once on the developers' machines and then distributed to the world. If a million copies are running, then we can be rest assured that they are running on a very large number of heterogeneous devices. These devices can be very different from each other. Of course, they will have to share the same ISA, but they can have radically different main memory sizes and even cache sizes. Unless we assume that all the  $2^n$  addresses are accessible to a program, no other assumption can be made. This may sound impractical on 64-bit machines, but this is the most elegant assumption that can be made. Of course, how we design a memory system whose size is much smaller than  $2^{64}$  bytes remains a problem to be solved.

What if we made another assumption? If we assumed that the program can access 2 GB at will, it will not run on a system with 1 GB of memory, unless we find a mechanism to do so. If we can find a mechanism to do this, then we can always scale the system to assume that an address is  $2^{32}$  or  $2^{64}$  bytes and still manage to run on physical systems with far lower memory. We thus have a *compatibility problem* here, where we want our program to assume that addresses are *n* bits wide (typically 32 or 64 bits), yet run on machines with all memory sizes (typically much lower than the theoretical maximum).

**Definition 2** Processes assume that they can access any byte in large memory regions of size  $2^{32}$  or  $2^{64}$  bytes at will (for 32-bit and 64-bit systems, respectively). Even if processes are actually accessing very little data, there is a need to create a mechanism to run them on physical machines with far lower memory (let's say a few GBs). The fact is that the addresses they assume are not compatible with physical addresses (on real machines). This is the compatibility problem.

Our simplistic assumption allows us to easily write a program, compile it, and also distribute the compiled binaries. Then when the processor runs it, it can also live with the same assumption and assume that the entire address space, which is very large in the case of a 64-bit machine, is accessible to the running program (process). All of this is subject to successfully solving the compatibility problem. There are unfortunately several serious problems that get introduced because of this assumption. The most important problem is that we can have multiple processes that are either running one after the other (using multitasking mechanisms) or are running in parallel on different cores. These processes can access the same address because nothing prohibits them from doing so.

#### The Overlap Problem

In this case, unbeknownst to both the processes, they can corrupt each other's state by writing to the same address. One program can be malicious and then it can easily get access to the other process's secrets. For example, if one process stores a credit card number, another process can read it straight out of memory. This is clearly not allowed and presents a massive security risk. Hence, we have two opposing requirements over here. First, we want an addressing mechanism that is as simple and straightforward as possible such that programs and compilers remain simple and assume that the entire memory space is theirs. This is a very convenient abstraction. However, on a real system, we also want different processes to access a different set of addresses such that there is no overlap between the sets. This is known as the *overlap problem*.

**Definition 3** Unless adequate steps are taken, it is possible for two processes to access overlapping regions of memory and also it is possible to get unauthorized access to other processes' data by simply reading values that they write to memory. This is known as the overlap problem.

## 2.2.1 Memory Map of a Process

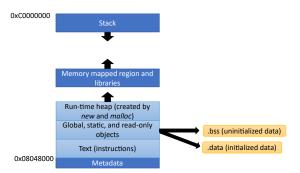

Let us continue assuming that a process can access all memory locations at will. We need to understand how it makes the life of the programmer, compiler writer and OS developer easy. Figure 2.7 shows the memory map of a process on the Linux operating system. The memory map is a layout of the memory space that a process can access. It shows where each type of data (or code) is stored.

Figure 2.7: The memory map of a process in 32-bit Linux