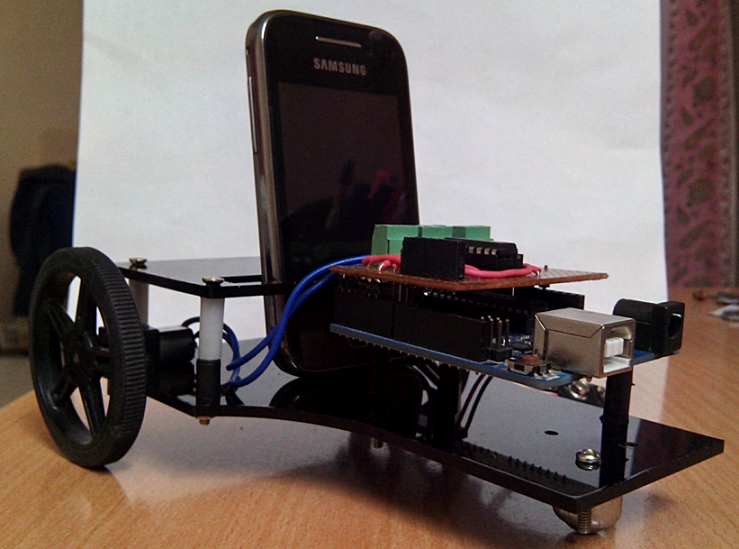

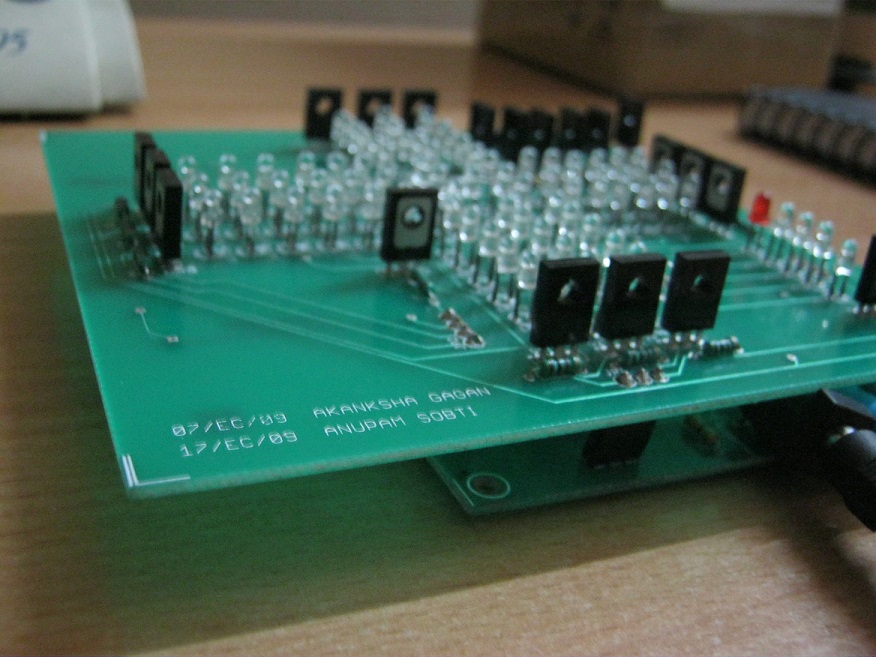

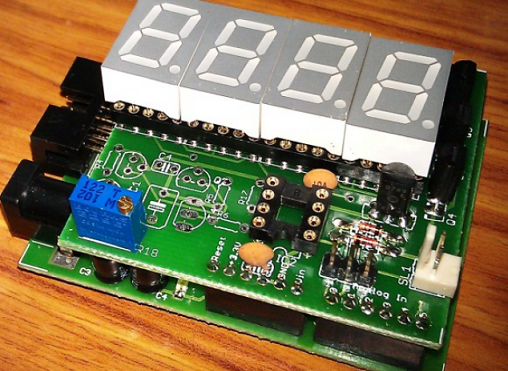

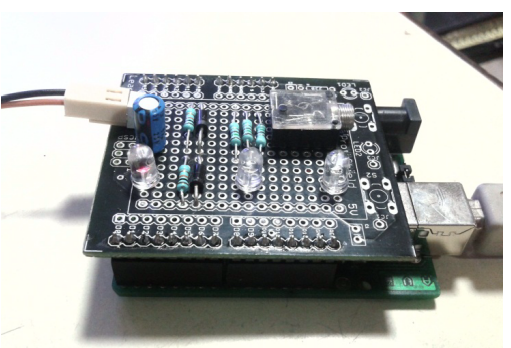

I use a mix of techniques from Computer Vision, Embedded Systems and Machine Learning for my work. My research interest is in smart edge devices that can be used in various sectors like healthcare, manufacturing, agriculture etc.

Current Location : New Delhi

Contact :

Education:

| PhD (Ongoing) | IIT Delhi | 2016- |

| M.Tech. (Microelectronics) | BITS Pilani (WILP) | 2014-16 |

| B.E. (ECE) | NSUT Delhi (formerly NSIT, DIT) | 2009-13 |

Work Experience:

| IIT Delhi | 2016- | Teaching Assistant |

| Assisted teaching and labs for courses on Embedded System Design, Digital Logic Design, Digital Systems Project Lab, Design of Cyber-physical systems | ||

| Qualcomm India (Bangalore) | 2013-16 | DFT Engineer |

| Responsible for Gate Level Simulations and Post-silicon bringup of Memory BIST and ATPG tests on various MSM and MDM devices Led the memory failure analysis team at Bangalore. | ||

Publications and Patents

Awards:

- Won the first prize in Cadence Tensilica Hackathon on "Porting deep neural networks on Tensilica AI Processors" along with team members, Ayushi Agarwal and Saurabh Tewari from IIT Delhi.

- Outstanding teaching assistant award for Embedded System Design (Sem II - 2016-17)

- Outstanding teaching assistant award for Digital Logic Design (Sem I - 2016-17)

Programming

- Expertise at Python/C++

- Working knowledge of MATLAB and Bash

Tools

- Tensorflow (Machine Learning Framework)

- PyTorch (Machine Learning Framework)

- VCS (Hardware simulation)

- Modelsim (Hardware simulation)

- Xilinx Vivado (FPGA Synthesis and Simulation)

- EAGLE (PCB Design)

Last update : May 2019